一、定義與劃分標(biāo)準(zhǔn)

(1)先進(jìn)制程(Advanced Prcess)

定義:指當(dāng)前技術(shù)前沿的半導(dǎo)體制造工藝,通常以晶體管柵極最小線寬(如納米/nm)為標(biāo)志。

典型范圍:

7nm及以下(如臺(tái)積電3nm、三星2nm、英特爾18A)。

部分場(chǎng)景下,14/16nm~7nm也被視為“準(zhǔn)先進(jìn)制程”。

核心特征:

使用FinFET(鰭式場(chǎng)效應(yīng)晶體管)或GAA(環(huán)柵晶體管)等三維結(jié)構(gòu)。

極紫外光刻(EUV)技術(shù)普及。

高晶體管密度(每平方毫米數(shù)億個(gè)晶體管)。

(2)成熟制程(Mature Prcess)

定義:技術(shù)已標(biāo)準(zhǔn)化、生產(chǎn)穩(wěn)定且成本較低的工藝,通常指28nm及以上的制程。

典型范圍:

28nm~180nm(如40nm、65nm、90nm等)。

部分特殊應(yīng)用(如功率半導(dǎo)體)仍使用微米級(jí)(μm)工藝。

核心特征:

平面晶體管(Planar FET)結(jié)構(gòu)為主。

深紫外光刻(DUV)技術(shù)即可滿(mǎn)足需求。

低研發(fā)成本,高良率(通常>95%)。

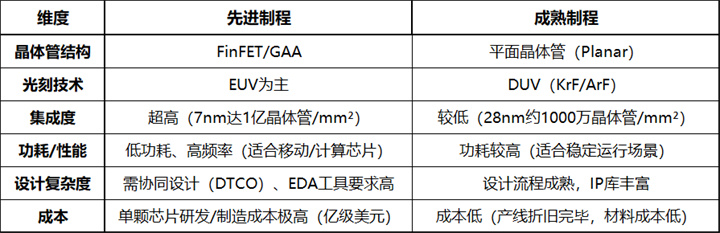

二、技術(shù)差異對(duì)比

三、應(yīng)用場(chǎng)景

先進(jìn)制程

高性能計(jì)算:CPU(如蘋(píng)果A系列)、GPU(NVIDIA)、AI芯片(如TPU)。

5G/6G通信:基帶芯片(高通驍龍)、射頻前端。

前沿領(lǐng)域:自動(dòng)駕駛芯片(特斯拉FSD)、量子計(jì)算接口芯片。

成熟制程

物聯(lián)網(wǎng)(IoT):傳感器、MCU(如STM32)。

汽車(chē)電子:ECU、電源管理芯片(PMIC)。

工業(yè)與家電:電機(jī)控制、顯示驅(qū)動(dòng)芯片。

模擬芯片:射頻、功率器件(如IGBT)。

(注:成熟制程占全球半導(dǎo)體產(chǎn)能的70%以上,尤其在汽車(chē)、工業(yè)領(lǐng)域需求持續(xù)增長(zhǎng)。)

四、先進(jìn)制成全球競(jìng)爭(zhēng)玩家介紹

2025年全球晶圓代工廠營(yíng)收占比,全球90%的晶圓代工營(yíng)收被五大晶圓代工廠占據(jù)。

目前,全球范圍內(nèi)在先進(jìn)制程領(lǐng)域競(jìng)爭(zhēng)的主要玩家包括臺(tái)積電、三星和英特爾。

臺(tái)積電(TSMC)約占66%,三星(Samsung)約占9%,聯(lián)電(UMC)、中芯國(guó)際(SMIC)、格羅方德(Global Foundries)各占5%。

臺(tái)積電已經(jīng)宣布成功大量量產(chǎn)3nm鰭式場(chǎng)效電晶體制程技術(shù),并正在推進(jìn)2nm和1nm技術(shù)的研發(fā)。三星也在積極發(fā)展其先進(jìn)制程技術(shù),規(guī)模生產(chǎn)3nm芯片已是多年前立下的目標(biāo)。

五、先進(jìn)制程技術(shù)演進(jìn)與產(chǎn)業(yè)影響分析

1. 多芯片互聯(lián)與超節(jié)點(diǎn)架構(gòu)在AI計(jì)算中的挑戰(zhàn)與發(fā)展

近年來(lái),半導(dǎo)體行業(yè)的核心關(guān)注點(diǎn)主要聚焦于單芯片算力的提升。然而,隨著AI大模型(如千億級(jí)參數(shù)模型)的快速發(fā)展,計(jì)算范式正逐步向多芯片互聯(lián)通信密集型架構(gòu)演進(jìn)。這一趨勢(shì)對(duì)低延遲互連技術(shù)(如chiplet、3D封裝)和跨節(jié)點(diǎn)并行計(jì)算能力提出了更高要求。

具體挑戰(zhàn)包括:

張量并行與專(zhuān)家模型分發(fā)對(duì)高帶寬、低延遲互聯(lián)的需求 ;

超節(jié)點(diǎn)(Super Node)架構(gòu)的興起,即通過(guò)提升單節(jié)點(diǎn)內(nèi)的計(jì)算與存儲(chǔ)資源密度優(yōu)化分布式訓(xùn)練效率 ;

能效比優(yōu)化成為關(guān)鍵,AI負(fù)載下的計(jì)算效率需結(jié)合制程微縮與架構(gòu)創(chuàng)新共同提升

2. 華為帶動(dòng)國(guó)產(chǎn)半導(dǎo)體產(chǎn)業(yè)鏈的協(xié)同發(fā)展

華為在先進(jìn)制程領(lǐng)域的突破顯著加速了國(guó)產(chǎn)半導(dǎo)體產(chǎn)業(yè)鏈的自主化進(jìn)程,具體表現(xiàn)為:

成熟制程需求回暖:2024年Q2模擬芯片(PMIC、信號(hào)鏈等)訂單超預(yù)期,主要驅(qū)動(dòng)力為工業(yè)與汽車(chē)客戶(hù)庫(kù)存回補(bǔ),8/12英寸晶圓廠產(chǎn)能利用率接近滿(mǎn)載,且增長(zhǎng)態(tài)勢(shì)有望延續(xù)至年底。

先進(jìn)制程研發(fā)加速:國(guó)內(nèi)頭部代工企業(yè)(如中芯國(guó)際)持續(xù)加大研發(fā)投入,預(yù)計(jì)2024H2起將進(jìn)入擴(kuò)產(chǎn)與技術(shù)迭代的關(guān)鍵階段,長(zhǎng)期競(jìng)爭(zhēng)力有望進(jìn)一步提升。

3. 國(guó)產(chǎn)半導(dǎo)體產(chǎn)業(yè)鏈的挑戰(zhàn)與結(jié)構(gòu)性機(jī)遇

受美國(guó)出口管制影響,國(guó)內(nèi)高性能計(jì)算芯片設(shè)計(jì)企業(yè)(如AI加速器、服務(wù)器CPU廠商)面臨晶體管規(guī)模限制,推動(dòng)對(duì)本土先進(jìn)制程產(chǎn)能的需求激增。

核心趨勢(shì)包括:

先進(jìn)制程稀缺性凸顯:盡管多家國(guó)內(nèi)廠商布局14nm及以下節(jié)點(diǎn),但技術(shù)領(lǐng)先者(如中芯國(guó)際N+1/N+2工藝)仍具備2年以上的代差優(yōu)勢(shì)。

設(shè)備鏈國(guó)產(chǎn)化提速:光刻、刻蝕、薄膜沉積等關(guān)鍵設(shè)備環(huán)節(jié)成為投資重點(diǎn),本土供應(yīng)鏈滲透率持續(xù)提升。

4. 半導(dǎo)體設(shè)備行業(yè)展望及核心標(biāo)的推薦

2024年國(guó)內(nèi)半導(dǎo)體設(shè)備行業(yè)經(jīng)歷階段性調(diào)整,當(dāng)前估值具備吸引力。

未來(lái)驅(qū)動(dòng)因素包括:

存儲(chǔ)技術(shù)迭代:2025年DRAM/NAND將進(jìn)入新制程周期,帶動(dòng)設(shè)備需求回升。

政策支持成熟制程擴(kuò)產(chǎn):以提升全球市場(chǎng)份額為目標(biāo),本土設(shè)備商(如北方華創(chuàng)、中微公司)將優(yōu)先受益。

5. 國(guó)產(chǎn)算力產(chǎn)業(yè)鏈的多環(huán)節(jié)協(xié)同突破

國(guó)產(chǎn)AI算力生態(tài)涵蓋設(shè)計(jì)、制造、封裝及配套硬件,核心環(huán)節(jié)包括:

PCB/封裝基板:深南電路、興森科技在高密度互連(HDI)領(lǐng)域技術(shù)領(lǐng)先。

芯片設(shè)計(jì):寒武紀(jì)、云天勵(lì)飛通過(guò)差異化架構(gòu)(如NPU+存算一體)提升性?xún)r(jià)比。

服務(wù)器集成:國(guó)產(chǎn)化率提升帶動(dòng)整機(jī)廠商份額增長(zhǎng)。

6. 華為384核超節(jié)點(diǎn)對(duì)國(guó)產(chǎn)算力板塊的催化作用

盡管產(chǎn)能爬坡短期制約放量,但華為Atlas 900超節(jié)點(diǎn)集群的推出標(biāo)志著國(guó)產(chǎn)算力架構(gòu)進(jìn)入新階段。

核心受益方向包括 先進(jìn)制造[中芯國(guó)際(14nm FinFET擴(kuò)產(chǎn))]和先進(jìn)封裝[兆易創(chuàng)新(HBMlike定制存儲(chǔ))。

7. 存儲(chǔ)芯片在算力基建中的核心地位

存儲(chǔ)帶寬已成為算力瓶頸突破的關(guān)鍵,行業(yè)趨勢(shì)包括: DDR5/LPDDR5滲透率提升;存算一體技術(shù):通過(guò)3D堆疊(如HBM)緩解"內(nèi)存墻"問(wèn)題。

六、總結(jié)

先進(jìn)制程是科技競(jìng)爭(zhēng)的制高點(diǎn),但依賴(lài)巨額投入和尖端設(shè)備。

成熟制程是半導(dǎo)體產(chǎn)業(yè)的“基石”,支撐絕大多數(shù)實(shí)際應(yīng)用。

未來(lái):兩者將長(zhǎng)期共存,先進(jìn)制程向3D集成(Chiplet)演進(jìn),成熟制程通過(guò)特色工藝(如BCD、SiC)煥發(fā)新生。