HBM 概述

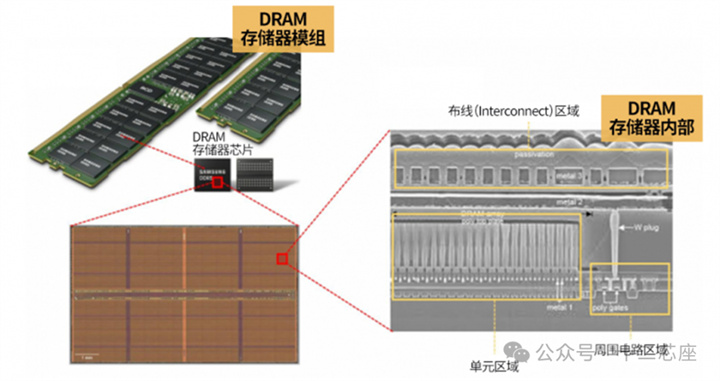

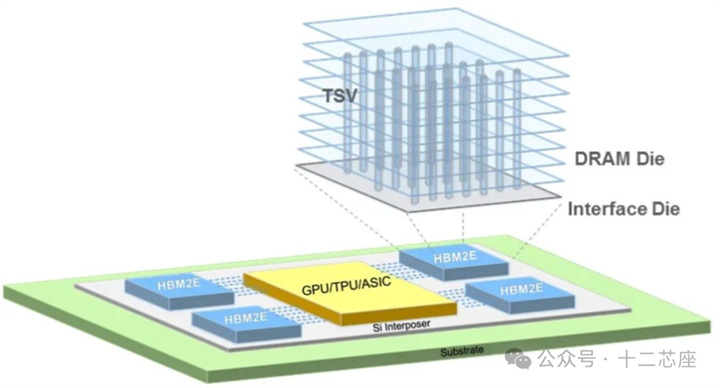

HBM(High Bandwidth Memory)是一種由AMD和SK hynix聯合開發的創新3D堆疊DRAM技術。該技術通過將多層DRAM芯片垂直堆疊,并利用高帶寬的串行接口實現與GPU或CPU的直連,從而提供遠遠超越傳統DRAM的帶寬和容量。高帶寬內存(HBM)它象征著內存技術的革命性跨越,尤其在高性能計算(HPC)、人工智能(AI)、數據中心和高端游戲等領域。

Memory 進化史

內存技術從早期的靜態隨機存取存儲器(SRAM)和動態隨機存取存儲器(DRAM)發展至今,經歷了多個關鍵階段:

SRAM 與 DRAM 的誕生 :SRAM 憑借高速訪問特性適用于緩存場景,而 DRAM 因高存儲密度和成本效益成為主內存的首選。

同步動態隨機存取存儲器(SDRAM) :為縮小內存與 CPU 速度差距而引入,實現單時鐘周期內數據讀寫。

雙倍數據率同步動態隨機存取存儲器(DDR SDRAM) :利用時鐘上升沿和下降沿傳輸數據,使數據傳輸速率翻倍。

多倍數據率技術的發展 :從 DDR 到 DDR2、DDR3、DDR4直到DDR5,內存數據傳輸速率持續提升,功耗和成本效益不斷優化。

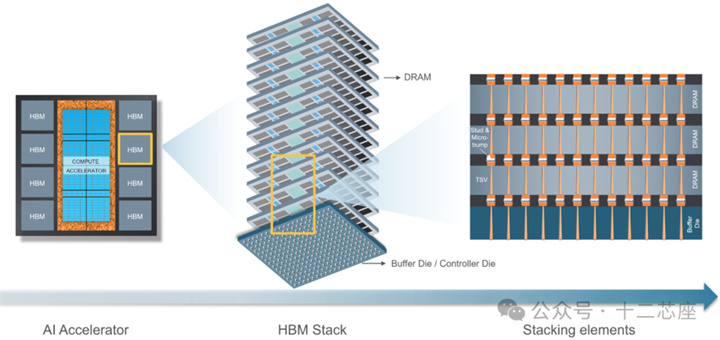

HBM 原理

HBM 原理HBM 的核心在于獨特的 3D 堆疊架構和 TSV(Through - Silicon - Via)技術:

3D 堆疊架構 :垂直堆疊多個 DRAM 芯片層,增加單位面積內存容量,各層 DRAM 通過微凸點與邏輯芯片相連。

TSV 技術 :在硅芯片中垂直貫穿導電通路連接不同層次電路,減少芯片間連接長度和電阻。

高帶寬串行接口 :與傳統并行接口相比,串行接口在更少引腳數量下實現更高數據傳輸速率。

HBM優勢

高帶寬 :滿足高性能計算需求,帶寬遠超傳統 DRAM。

高容量 :3D 堆疊技術在相同芯片面積內集成更多 DRAM 層,提供更大內存容量。

低功耗 :垂直堆疊結構減少數據傳輸距離,TSV 技術也有助于降低功耗。

小尺寸 :3D 堆疊設計使內存模塊尺寸大幅減小,利于系統緊湊設計。

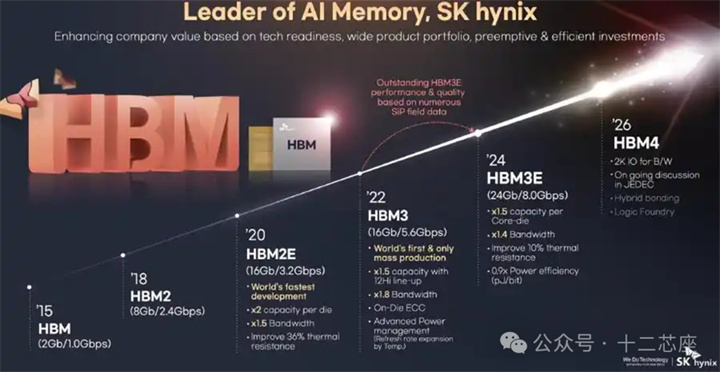

HMB技術發展歷程

2013年:

AMD 與 SK hynix宣布合作開發 HBM 技術。

2015 年:

HBM 技術的開端,當時的帶寬為 1.0Gbps,容量為 2Gb。

2018年:

容量提升至 8Gb,帶寬升至 2.4Gbps。它是世界上發展最快的版本,相比前代,每芯片容量翻倍、帶寬提升 1.5 倍,熱阻也提升了 34%。

2020年:

容量和帶寬達到 16Gb 和 3.2Gbps。其在速度和容量上均有顯著增強。

2022年:

帶寬提升至 5.6Gbps,SK 海力士實現了全球首次量產。該技術具備 1.5 倍的容量提升、1.8 倍的帶寬提升、1.2Hi 連接,還采用了芯片上芯片(On-Die)、先進電源管理(通過 Temp.管理)等技術。

2024年:

容量達到 24Gb,帶寬高達 8.0Gbps。其每芯片容量提升 1.5 倍,帶寬提升 1.4 倍,并且熱阻改善了 10%,能效達到 0.9x(pJ/bit)。

2026年:

計劃在 2026 年推出 HBM4 技術,將在 JEDEC 標準下進行討論,采用混合鍵合技術以及邏輯晶圓廠生產。

總結

高帶寬內存(HBM)作為現代計算領域的一項革命性技術,憑借其獨特的 3D 堆疊架構和 TSV 技術,在性能、容量、功耗和尺寸等方面實現了全方位突破。自 2013 年問世以來,HBM 經歷了多次迭代升級,從最初的 1.0Gbps 帶寬到如今的 8.0Gbps,不僅推動了高性能計算、人工智能、數據中心等領域的快速發展,也為未來的技術演進奠定了堅實基礎。展望未來,隨著 HBM4 技術的逐步落地,這一技術將繼續引領內存發展的潮流,為人類社會的智能化進程注入更強動力。